## SVPWM CONTROL OF THREE-PHASE MULTILEVEL DECENTRALIZED POWER CONVERTERS

Phu Cong Nguyen<sup>1,\*</sup>, Khac Sinh Le<sup>1</sup>, Quoc Dung Phan<sup>2</sup>

<sup>1</sup>*Ho Chi Minh City University of Industry and Trade*

<sup>2</sup>*Ho Chi Minh City University of Technology*

\*Email: [congnp@huit.edu.vn](mailto:congnp@huit.edu.vn)

Received: 6 November 2024; Revised: 19 November 2024; Accepted: 24 February 2025

### ABSTRACT

This paper presents a method for implementing decentralized space vector pulse width modulation (SVPWM) (DSVPWM) for a three-phase multilevel power converter (TPMPC). The three-phase power converter discussed in this study has a dynamic refactor consisting of multiple cascade modules connected in series in each phase. Each module consists of a cascade dynamic circuit and a local controller. Local controllers will establish a limited number of communications with neighboring controllers, the communication signal used are row and column position cells, reference voltage amplitude, and reference voltage frequency. The DSVPWM method can be considered as a multi-level modulation technique, which can be automatically adjusted based on the number of modules operating in the converter. The execution program of each local module shows a lower number of calculations compared to the power converter using a central controller. The proposed power converter can automatically adjust the dynamic refactoring when a fault occurs to meet the flexibility in control and improve the continuity of power supply in operation. The proposed model and modulation algorithm are analyzed, tested on Matlab/Simulink software.

**Keywords:** Decentralized control, decentralized SVPWM, multilevel power converter, cascade full bridge converter.

### 1. INTRODUCTION

The emergence and development of power converters is closely linked to the development of microprocessors. Typically, power converters use a microprocessor as a central controller [1]. As power converters develop, the central processor must increasingly have high processing speed, large connectivity and control capabilities [2]. This is sometimes an obstacle to the design of multi-level power converters and in some cases can lead to quite high processor costs. The core feature when using a central controller is to concentrate all calculations in a single entity. During operation, if an error occurs (loss of connection signal, power error, phase loss, etc.), the system must stop immediately and it takes a relatively long time to re-establish the connection and correct the program. Therefore, flexibility in operation and continuity in power supply may not be achieved. Although it is known that advances in technology and manufacturing techniques allow the production of microprocessors with increasingly high computing speed and connectivity. However, the expansion of control connectivity and processing speed still has certain limitations in the design and manufacture of microprocessors.

The trend of designing power converters in modular form is increasingly interested [3-5]. The modular structure allows power converters to operate flexibly, easily to maintain and repair when necessary. In the power converter, modules in the form of half bridge [4], full bridge cascade [6], flying capacitor can be connected in series [7,8]. The number of modules connected in series in each phase allows to adjust the voltage amplitude, the number of voltage levels, the switching voltage level... thereby achieving the criteria of voltage quality and power on the load. The pinnacle of the modular structure is used in the decentralized control structure of multilevel power converters. Each module will include a local controller to calculate the necessary switching pulses to directly control the power keys of that module. It can be said that the tasks of the central controller (for centrally controlled

power converters) will be divided for each module in the distributed power converters. Microprocessors with large size, speed and computational capacity are replaced by local processors with low computational requirements and control connectivity [9].

Multilevel modulation techniques have been developed around two main methods: carrier pulse width modulation (CPWM) [10–14] and SVPWM [1,15,16]. The CPWM includes phase shift (PS), phase disposition (PD), phase opposition disposition (POD),... which are processed on an analog technical platform. The switching pulse of each module is calculated and processed in each individual phase of the power converter. Meanwhile, the space vector pulse width dynamic modulation method is processed on a digital platform. The switching pulse of each power switch is calculated in a single central whole, which is convenient for establishing improvements related to the output power quality. Therefore, the SVPWM method shows that it is very suitable for deployment on current microprocessors. The multilevel modulation method using SVPWM technique has been deployed for single phase, three-phase, and multiphase power converter structures; In which, three-phase is the most typical case, with the most applications in industry and civil.

Studies on decentralized control power converters using CPWM have given some very promising results, including: using the PS method for multi-module parallel structures to perform DC/DC modulation [17,18]; using the PS method for multi-module capacitor coupling to perform DC/DC and DC/AC modulation [17,19]; using the PS method for multi-module half bridge and full bridge cascade structures to perform DC/AC modulation [20]. Each module has synthesized for itself carrier waves with appropriate frequencies and amplitudes based on receiving information about carrier amplitude [20], carrier phase angle [18], position... of neighboring modules [20]. Meanwhile, studies on decentralized control power converters using SVPWM have only had some initial results but are very promising and have many prospects in the future.

Based on the structure and the quality index to be achieved, there are many ways to implement SVPWM technique for multilevel power converters. The first method that can be considered is to divide the vector space to be modulated into each modulation region and apply specific algorithms to each modulation region to achieve the desired power quality [21]. This method has the advantage of being able to accurately impact each smallest specific region in the multilevel space vector. However, this leads to a complex calculation process and is often applied to structures with predetermined levels, making it difficult to develop and expand when the number of voltage levels increases. The second method is introduced as a general modulation method for structures with any number of voltage levels [9,22]. This study is conducted by converting the vector space from multilevel to two level vector space, calculating the necessary switching parameters and then converting to multilevel space to determine the required switching vector and switching time. In addition, as the number of modules increases, the number of modulation voltage levels increases, resulting in a very large number of microprocessor calculations. This is a common problem when power converters are designed with a central controller.

This study introduces the connection and control diagram between local controllers; and method of switching pulse modulation for a decentralized TPMPC based on SVPWM technique. The proposed structure and method of DSVPWM show that the computational volume of each local controller is greatly reduced when compared to classical power converters with a central controller. The research proposal allows for quick and convenient dynamic adjustment of the power converter structure to ensure flexibility in control and optimization when necessary. The switching pulses provided to the full bridge cascade power switches are calculated by the local controllers when they aggregate: voltage amplitude and frequency from other controllers; controller position in phase and phase position; total number of controllers that are active. A decentralized three-phase, 13-level cascade converter model is built in Matlab/Simulink software to verify the proposals.

## 2. THE SVPWM METHOD FOR LOCAL CONTROLLERS OF DECENTRALIZED POWER CONVERTERS

### 2.1 Proposed structure

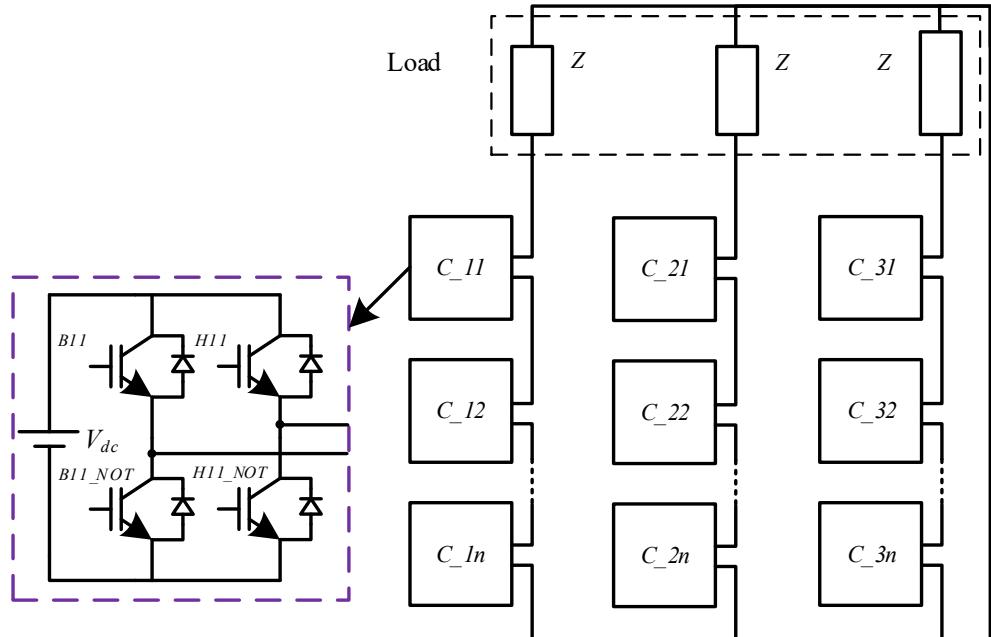

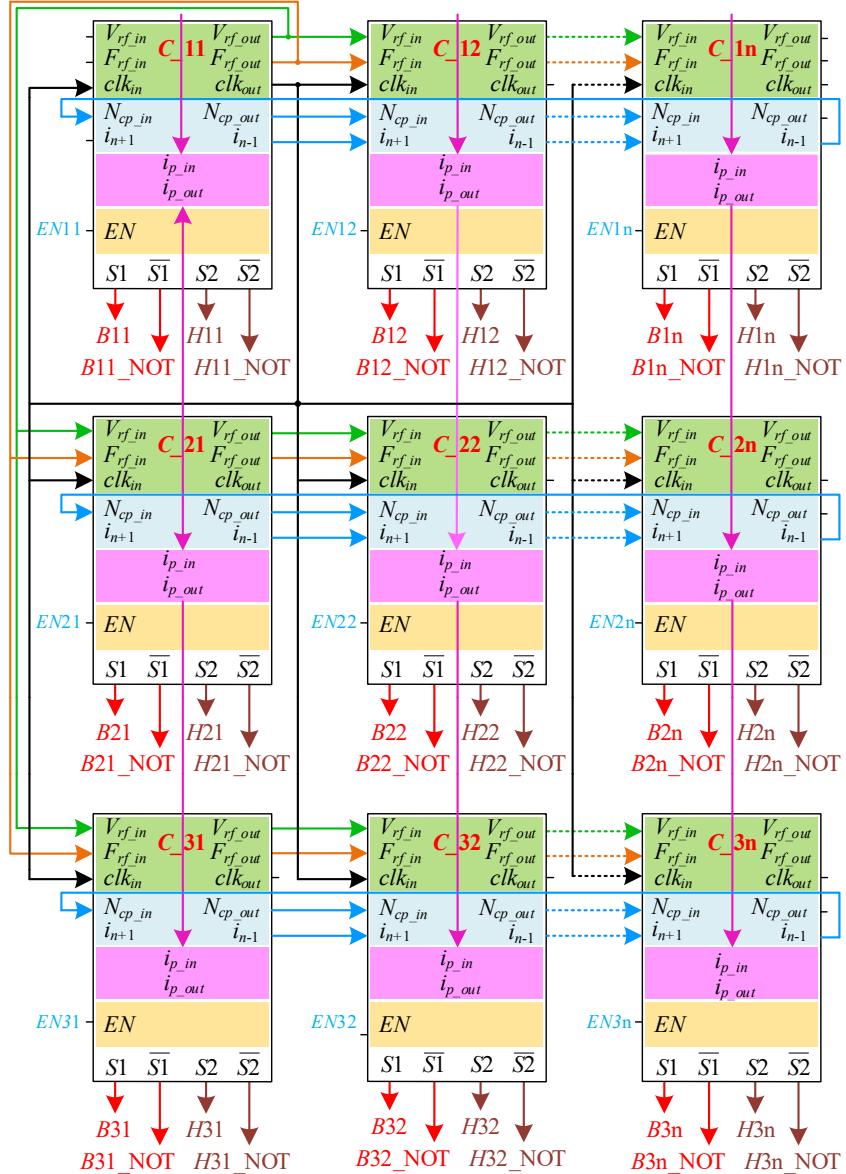

Figure 1 shows the interconnection structure of the IGBTs of the cells together, each cell has 4 IGBTs connected in a cascade structure, each cell has used a DC voltage source with a constant amplitude  $V_{dc}$ . Meanwhile, a proposed communication proposal for the decentralized control TPMPC

is shown in Figure 2. The number of signals and control functions used by each local controller are shown in Table 1. The *EN* signal enables a cell to work or stop working.

## 2.2 Proposed SVPWM algorithm

Where  $i_p$  is the position information of the cell in the phases,  $p$  is the total phases of the inverter (in this study  $p = 3$ ). To determine the location of the cell in which phase, the study uses a simple sequential numbering method as presented in equations (1), (2). Cells at phase  $a$  have no information about the previous cell so  $i_{p\_in} = 0$ .

$$i_{p\_out}^k = i_{p\_in}^k + 1 \quad (1)$$

$$i_p^k = i_{p\_out}^k \quad (2)$$

Figure 1. Connection diagram of insulated gate bipolar transistor (IGBT) modules

Table 1. The signal pins of one cell

| Symbol                       | Description                                                     |

|------------------------------|-----------------------------------------------------------------|

| EN                           | Enable or disable cell operation                                |

| $V_{rf\_in}$                 | Get signal reference voltage from the previous cell             |

| $F_{rf\_in}$                 | Get reference frequency from the previous cell                  |

| $i_{n+1}$                    | Get position information from the previous cell in a phase      |

| $i_{n-1}$                    | Transmitted position information to the next cell in a phase    |

| $i_{p\_in}$                  | Get position information from the previous cell in a column     |

| $i_{p\_out}$                 | Transmitted position information to the next cell in a column   |

| $N_{cp\_in}$                 | Get total cells information from the previous cell in a phase   |

| $N_{cp\_out}$                | Transmitted total cells information to the next cell in a phase |

| $clk_{in}, clk_{out}$        | Synchronous pulse transmission and reception                    |

| $V_{rf\_out}$                | Transmitted reference voltage to next cell in a phase           |

| $F_{rf\_out}$                | Transmitted reference frequency to the next cell in a phase     |

| $S1, \bar{S1}, S2, \bar{S2}$ | The PWM control                                                 |

Figure 2. Communication between local controllers with DSVPWM method

A similar procedure is established to calculate the position of cells  $i_n^k$  in each phase as shown in equations (3)-(5). The first cell in each phase has no information so  $i_{n+1}^k = 0$ . The position information of the last cell in each phase is the total active local controllers  $N_{cp}^k$ , this signal is transmitted from the first cell to the last cell in each phase.

$$i_{n-1}^k = i_{n+1}^k + 1 \quad (3)$$

$$i_n^k = i_{n-1}^k \quad (4)$$

$$N_{cp}^k = N_{cp\_out}^k = N_{cp\_in}^k \quad (5)$$

The positive-sequence reference voltages for the three-phase multilevel inverter can be expressed by (6), where  $V_{rf\_in}$  denotes the amplitude of the reference signal:

$$v_{ref}^k = \begin{cases} V_{rf\_in} \sin(\omega t) \\ V_{rf\_in} \sin(\omega t + \frac{2\pi}{3}) \\ V_{rf\_in} \sin(\omega t + \frac{4\pi}{3}) \end{cases} \quad (6)$$

Under the multilevel SVPWM scheme, as shown in equation (7), the modulation voltage at the output can be interpreted as an integer multiple of the voltage amplitude provided by a single cell.

$$v_r^k = \frac{v_{ref}^k}{V_{dc}^k} = [v_{r1}^k \quad v_{r2}^k \quad v_{r3}^k]^T \quad (7)$$

In equation (8), the floor(x) operator is applied to extract the integer portion of the reference voltage, whereas equation (9) determines its fractional component. The resulting fractional values  $v_f$  are then sorted in descending order, as defined in (10).

$$v_i^k = \text{floor}(v_r^k) \quad (8)$$

$$v_f^k = v_r^k - v_i^k \quad (9)$$

$$v_{fs}^k = \text{sort}(v_f^k) = [v_{fs1}^k \quad v_{fs2}^k \quad v_{fs3}^k]^T \quad (10)$$

The matrix A of dimension 1x4 is derived, with its entries determined by expression (11), (12). The matrix D is then introduced as specified in (13).

$$A^k = [0 \quad A_2^k \quad A_3^k \quad A_4^k] \quad (11)$$

$$A_g^k = \begin{cases} 1 & \text{if } [v_f(i_p^k, I)] = v_{fs}(g, I) \\ 0 & \text{if } [v_f(i_p^k, I)] \neq v_{fs}(g, I) \end{cases} \quad (12)$$

with  $g = 2 : 4$

$$D^k = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 0 & 1 & 1 & 1 \\ 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 \end{bmatrix} \quad (13)$$

The switching vector for the 2-level modulation stage is subsequently determined as expressed in (14).

$$v_d^k = A^k D^k = [v_{d1}^k \quad v_{d2}^k \quad v_{d3}^k \quad v_{d4}^k] \quad (14)$$

In the last step, the switching vector  $v_s$  is specified by equation (15). The associated switching intervals  $t_s$  are subsequently derived from the set of relations given in (16)-(20).

$$v_s^k = v_d^k + v_i^k(i_p^k, I) = [v_{s1}^k \quad v_{s2}^k \quad v_{s3}^k \quad v_{s4}^k] \quad (15)$$

$$t_s^k = [t_{s1}^k \quad t_{s2}^k \quad t_{s3}^k \quad t_{s4}^k] \quad (16)$$

$$\sum_{u=1}^{u=p+I} t_{su}^k = I \quad (17)$$

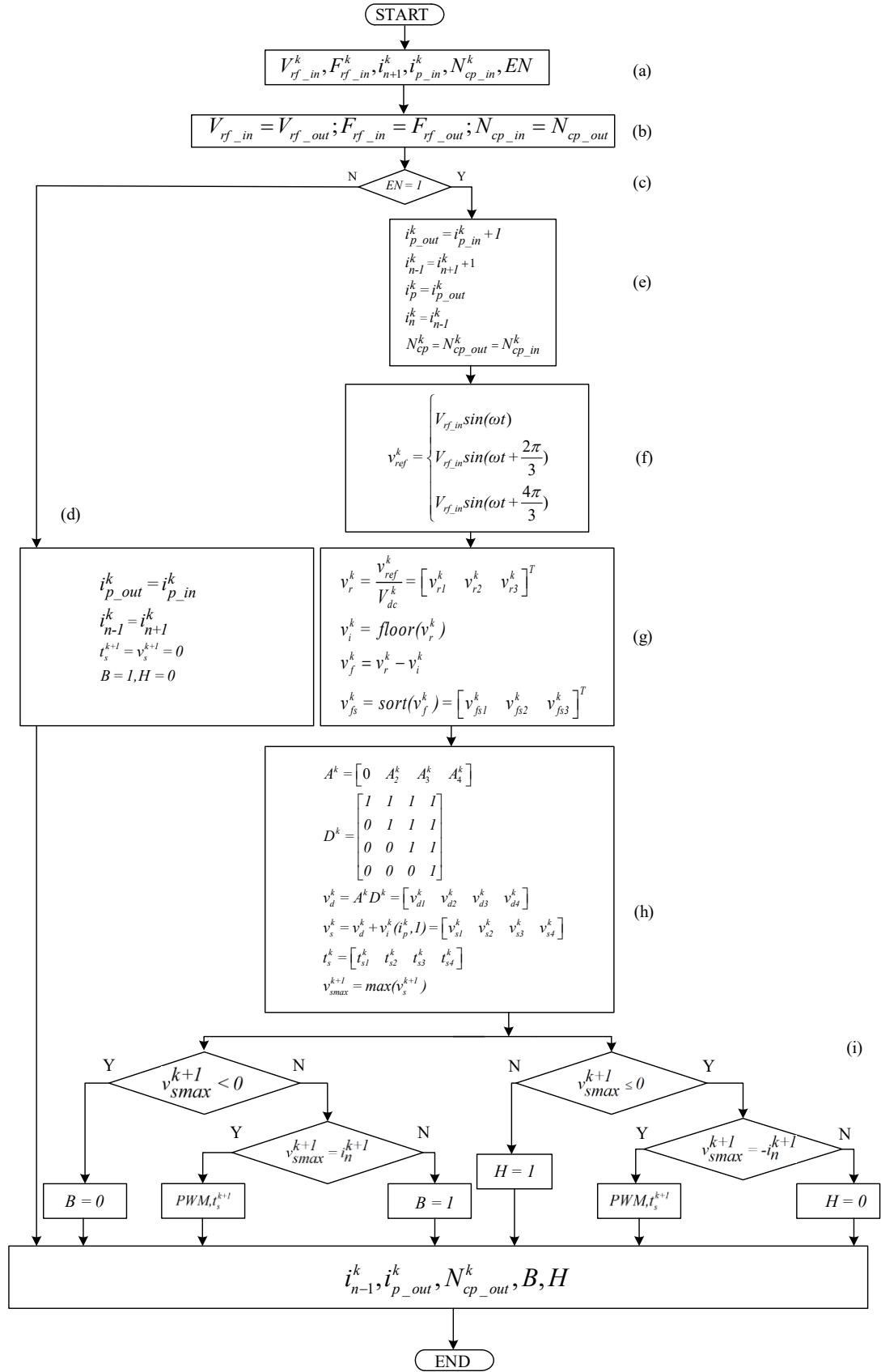

Figure 4. Program execution flowchart of each cell with DSVPWM method

$$t_{sI}^k = 1 - v_{fs}^k(1,1) \quad (18)$$

$$t_{p+1}^k = v_{fs}^k(p+1,1) \quad (19)$$

$$t_j^k = v_{fs}^k(j-1,1) - v_{fs}^k(j,1) \quad (20)$$

with  $j = 2 \div 3$

The largest element in the  $v_s$  vector is determined using the function  $\max(x)$  as (21)

$$v_{smax}^k = \max(v_s^k) \quad (21)$$

$$B = \begin{cases} 0 & \text{if } v_{smax}^k < 0 \\ 1 & \text{if } (v_{smax}^k > 0) \text{ and } (v_{smax}^k \neq i_n^k) \\ \text{PWM}(t_s^k) & \text{if } (v_{smax}^k > 0) \text{ and } (v_{smax}^k = i_n^k) \end{cases} \quad (22)$$

$$H = \begin{cases} 1 & \text{if } v_{smax}^k > 0 \\ 0 & \text{if } (v_{smax}^k \leq 0) \text{ and } (v_{smax}^k \neq -i_n^k) \\ \text{PWM}(t_s^k) & \text{if } (v_{smax}^k \leq 0) \text{ and } (v_{smax}^k = -i_n^k) \end{cases} \quad (23)$$

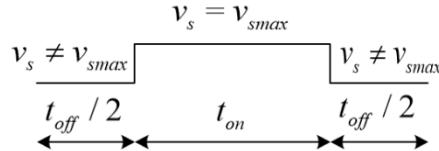

As depicted in Figure 1, the IGBTs within each module operate according to the control signals defined in equations (22) and (23). A value of  $B = 1$  commands the device to conduct, whereas  $B = 0$  forces it into the non-conducting state. For all other operating modes, the IGBT switching behavior is governed directly by the PWM waveform. The switching sequence of a PWM signal is illustrated in Figure 3, where the corresponding conduction  $t_{on}$  and turn-off durations  $t_{off}$  are determined using equations (24) and (25).

Figure 3. Trigger signal

$$t_{on} = \sum_{u=1}^{u=p+1} t_{su} \text{ if } (v_{su}^k = v_{smax}^k) \quad (24)$$

$$t_{off} = 1 - t_{on} \quad (25)$$

In the proposed structure and modulation method, the output voltage is the voltage contribution of the cells that are still operating in the TPMPC, the output phase voltage has the largest amplitude satisfying equation (26). Where  $m$  be the modulation index,  $m$  is determined according to equation (27). The control program of each cell is performed according to the algorithm flowchart of Figure 4.

$$v_{out\_max} = N_{cp} * V_{dc} \quad (26)$$

$$m = \frac{v_m}{V_{dc}} \quad (27)$$

Table 2. The number calculations in a PWM cycle of SVPWM and DSVPWM technique

| Calculation process | SVPWM technique                                                                 | DSVPWM technique                                                                              |

|---------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| vref                | vref is an 3-by-1 matrix                                                        | vref is an 3-by-1 matrix.                                                                     |

|                     | $N_{c1} = 3$                                                                    | $N_{d1} = 3$                                                                                  |

| vr                  | vr is an p-by-1 matrix                                                          | vr is an 3-by-1 matrix                                                                        |

|                     | $N_{c2} = 3$                                                                    | $N_{d2} = 3$                                                                                  |

| vfs                 | vfs is an 4-by-1 matrix                                                         | vfs is an 3-by-1 matrix                                                                       |

|                     | $N_{c3} = 4$                                                                    | $N_{d3} = 3$                                                                                  |

| vd                  | P is an 4-by-4 matrix                                                           | A is an 1-by-4 matrix                                                                         |

|                     | $N_{c4} = 4^2$                                                                  | $N_{d4} = 4$                                                                                  |

|                     | Permutation matrix P<br>$N_{c5} = 4^2$                                          | $N_{d5} = 0$                                                                                  |

|                     | vd is the product of two matrices 4-by-4                                        | vd is the matrix product of 1-by-4 and 4-by-4                                                 |

|                     | $N_{c6} = \frac{7}{8}4^3$<br>$N_{c7} = \frac{7}{8}4^2 \cdot 2 + \frac{9}{2}4^2$ | $N_{d6} = \frac{7}{8}4^2$<br>$N_{d7} = \frac{7}{8}4 \cdot 3 + \frac{5}{4}4^2 + \frac{13}{4}4$ |

| vs                  | vd is an 3-by-4 matrix                                                          | vd is a 1-by-4 matrix                                                                         |

|                     | vs is the sum of two matrices 3-by-4                                            | vs is the sum of two matrices 1-by-4                                                          |

|                     | $N_{c8} = 3 \cdot 4$                                                            | $N_{d8} = 4$                                                                                  |

| ts                  | vs is an 3-by-4 matrix                                                          | vs is a 1-by-4 matrix                                                                         |

|                     | ts is an 3-by-4 matrix                                                          | ts is a 1-by-4 matrix                                                                         |

|                     | $N_{c9} = 3 \cdot 4$                                                            | $N_{d9} = 4$                                                                                  |

### 2.3 Evaluation of the computational requirements per PWM cycle for SVPWM and DSVPWM schemes

Expressions (28) and (29) [23] specify the number of arithmetic operations involved in multiplying and adding the matrices A(x,y) and B(y,z). Using these expressions, Table 2 presents the computational requirements for each modulation stage of the conventional SVPWM method [24] and the proposed DSVPWM scheme. The results indicate that one switching cycle of SVPWM requires a total of 222 calculations, whereas the proposed method completes the cycle with only 64 calculations. This corresponds to a reduction in computational effort by a factor of about 3.5.

$$N_{mul} = \frac{7}{8}xyz \quad (28)$$

$$N_{add} = \frac{7}{8}x(y-2)z + \frac{5}{4}xy + \frac{5}{4}yz + \frac{8}{4}xz \quad (29)$$

## 3. SIMULATION RESULTS AND DISCUSSION

### 3.1 Configuration and simulation parameters

The three-phase, 13-level power converter is built on Matlab software; each phase has 6 full cells connected in series; Simulation parameters are shown in Table 3. Simulations of TPMPC operation to analyze the main issues:

- The ability to automatically configure the system in the normal operating state, the cells will accurately determine their own position in the phases and the phase position that the cell is locating.

- The system can accurately construct the output voltage so that it matches the prescribed reference voltage.

Table 3. Simulation parameters

| Parameter               | Symbol          | Unit     | Value     |

|-------------------------|-----------------|----------|-----------|

| DC voltage of each cell | Vdc             | V        | 100       |

| Modulation index        | m               |          | 5.8       |

| Load                    | L               | H        | 0.01      |

|                         | R               | $\Omega$ | 10        |

| Switching frequency     | fsw             | kHz      | 10        |

| Reference frequency     | Fr <sub>f</sub> | Hz       | 50        |

| Sampling time           | T <sub>s</sub>  | s        | $10^{-6}$ |

- The system is capable of automatically adapting its dynamic refactoring when cells are added to or removed from the phases. Each cell updates its position within the corresponding phase, along with the information regarding the total number of active cells. As a result, the output voltage is synthesized accurately based on the voltage contribution of each active cell.

### 3.2 Simulation results

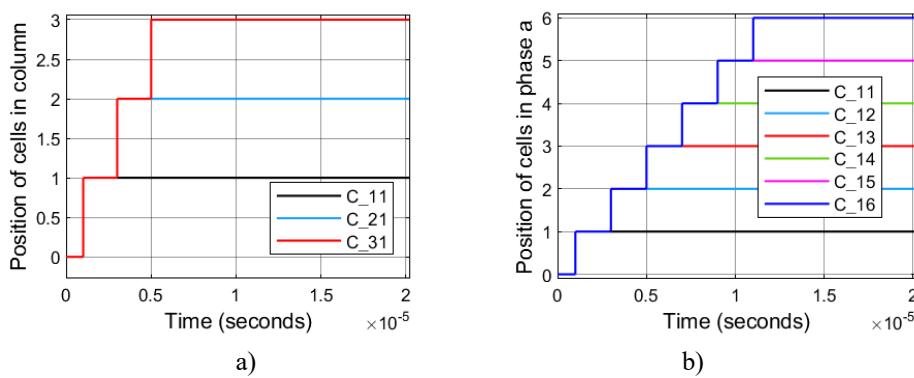

Figure 5 shows the process of cells determining their own positions in phases and columns. After three calculation steps, the cells have determined their phase positions, and after six calculation steps, the cells have determined their own positions in cells.

In the structure of a TPMPC, the number of cells in each phase is usually larger than the number of phases, so the time it takes for the system to complete configuration from start-up may be calculated by the number of cells in the phases. Therefore, the configuration time of the  $N_c$  system can be calculated as equation (30).

$$N_c = N_{cp} \quad (30)$$

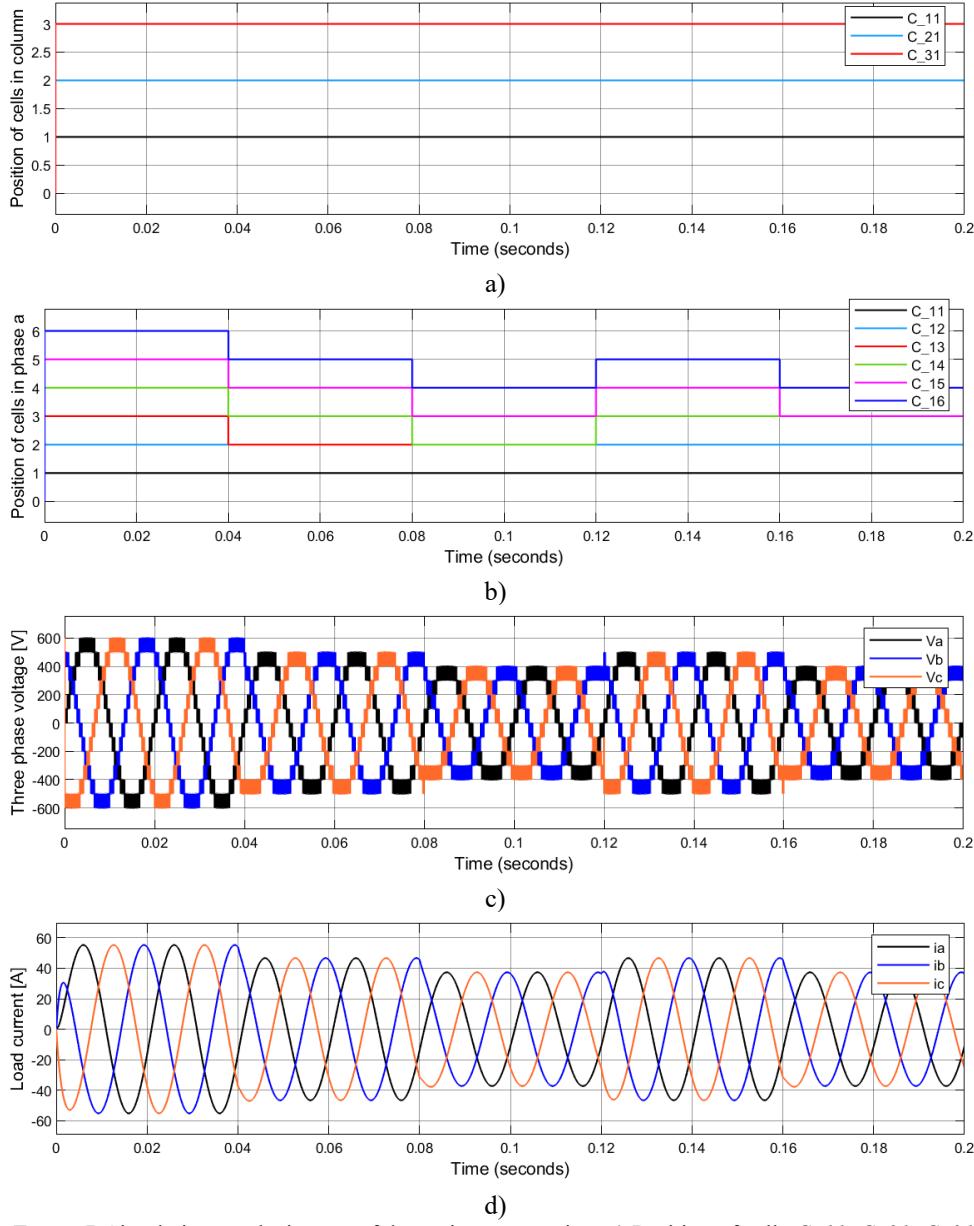

At start-up, the power converter operates with full cells, modulation index  $m = 5.8$ , reference frequency is 50Hz. Then, the simulation process is carried out as described in Figure 6. Figure 7 presents the simulation results showing the cell positions in phase and column, phase voltage and load current waveforms. With six cells contributing to each phase, the output phase voltage achieves 13 distinct levels, and its frequency responds exactly to the specified reference frequency.

At 0.04 seconds, three cells C\_13, C\_23, C\_33 stop working, the signals to the stopped cells will be transmitted directly from the input to the output, the 5 active cells in each phase quickly adjust their own positions, re-determine the appropriate switching vectors and switching times. The output phase voltage has 11 levels as the voltage contribution of the 5 cells, the maximum reference voltage amplitude that can be achieved is 500V.

The simulation results show that the voltage switches to a stable new state very quickly, and the transition process has no significant impact on the required voltage quality.

Figure 5. Position of cells; a) Position of cells C\_11, C\_21, C\_31; b) Position of cells C\_11, C\_12, C\_13, C\_14, C\_15, C\_16.

Figure 6. Simulation process

Figure 7. Simulation results in case of dynamic restructuring; a) Position of cells C\_11, C\_21, C\_31; b) Position of cells C\_11, C\_12, C\_13, C\_14, C\_15, C\_16; c) Three-phase voltage; d) Load current

At 0.08 seconds, four cells C\_14, C\_24, C\_34 continue to be removed, the remaining cells in the phases quickly adjust to the new state, the position of cell C\_11 is 1, the position of cell C\_12 is 2, the position of cell C\_15 is 3, the position of cell C\_16 is 4, as shown in Figure 7a. The remaining phase voltage is a maximum of 400V, there are 9 levels, the difference between the levels is still exactly 100V, the voltage frequency responds exactly to the reference frequency of 50Hz. This simulation result also

shows the same in the period from 0.16 seconds to 0.2 seconds when the TPMPC has 4 active cells in each phase.

At 0.12 seconds, the cells  $C_{13}$ ,  $C_{23}$ ,  $C_{33}$  are reinserted to continue working, each phase has 5 active cells, the output voltage has 11 levels, the position of the cells is quickly adjusted and rearranged from 1 to 5, the voltage between two levels is still stable with a value of 100V.

The tests have shown that during operation, the DSVPWM method and the proposed structure can ensure that the system performs dynamic refactoring, the TPMPC does not require to stop operating. This is one of the factors affecting the reliability and operation of the energy conversion system.

#### 4. CONCLUSIONS

The decentralized three-phase multilevel power converter using SVPWM method has been successfully used to find the switching pulse for each local cell. The calculation program of each cell shows a significant reduction in the amount of calculations when compared to the use of a central controller, which opens up the prospect of using low-speed and low-computation microprocessors in the design of power converters. The proposed decentralized power converter also shows the ability to automatically adjust the dynamic refactoring in case of adding or removing a cell, which contributes to increased operational flexibility and reliability in the ability to provide continuous, uninterrupted power. The content presented in this paper is limited to the analysis and evaluation on the simulation model. This research direction will continue to be considered and implemented on the experimental model, the detailed analysis and evaluation when implemented on the experimental model will be conducted and published in the coming time.

**Acknowledgements:** This work was funded by Ho Chi Minh City University of Industry and Trade (Contract number 06/HĐ-DCT dated January 9, 2024).

#### REFERENCES

1. Chikondra B., Muduli U.R., Behera R.K. - Performance Comparison of Five-Phase Three-Level NPC to Five-Phase Two-Level VSI. *IEEE Trans. Ind. Appl.* **56** (2020) 3767–3775. <https://doi.org/10.1109/TIA.2020.2988014>.

2. Sánchez Ó.L. - Space Vector Pulse-Width Modulation for Multilevel Multiphase Voltage-Source Converters. Ph.D. dissertation, Department of Electronic Technology, Universidad de Sevilla, Seville, Spain, (2008).

3. Roknuzzaman M., Yamaji T., Nakata H., Hamasaki S.I. - Power Flow Control using Modular Multilevel Converter with circulating current control for 3-phase AC/AC Conversion. *23rd Int. Conf. Electr. Mach. Syst.* **2020** (2020) 597–602. <https://doi.org/10.1109/SPEEDAM48782.2020.9161940>.

4. Mora A., Urrutia M., Cardenas R., Angulo A., Espinoza M., Diaz M., Lezana P. - Model-predictive-control-based capacitor voltage balancing strategies for modular multilevel converters. *IEEE Trans. Ind. Electron.* **66** (2019) 2432–2443. <https://doi.org/10.1109/TIE.2018.2844842>.

5. Martinez-Rodrigo F., Ramirez D., Rey-Boue A.B., De Pablo S., Herrero-De Lucas L.C. - Modular multilevel converters: Control and applications. *Energies* **10** (2017) 1–26. <https://doi.org/10.3390/en10111709>.

6. Luna B.E.D.O.B., Jacobina C.B., Oliveira A.C., Da Silva I.R.F.M.P. - Modeling and control of the modular multilevel cascade converter based on chopper-cells for grid-connected photovoltaic systems. *2015 IEEE Energy Convers. Congr. Expo.* **2015** (2015) 6877–6880. <https://doi.org/10.1109/ECCE.2015.7310623>.

7. Malidarreh P.B., Khaburi D.A., Rodriguez J. - Capacitor Voltage Imbalance Reduction in Flying Capacitor Modular Multilevel Converters by using Model Predictive Control. *2020 11th Power Electron. Drive Syst. Technol. Conf.* **2020** (2020) 2–5. <https://doi.org/10.1109/PEDSTC49159.2020.9088411>.

8. Jiao D., Huang Q., Huang A.Q. - Evaluation of Medium Voltage SiC Flying Capacitor Converter and Modular Multilevel Converter. ECCE 2020 - IEEE Energy Convers. Congr. Expo. (2020) 4386–4392. <https://doi.org/10.1109/ECCE44975.2020.9235758>.

9. Lopez O., Alvarez J., Malvar J., Yepes A.G., Vidal A., Baneira F., Perez-Estevez D., Freijedo F.D., Doval-Gandoy J. - Space-Vector PWM with Common-Mode Voltage Elimination for Multiphase Drives. IEEE Trans. Power Electron. **31** (2016) 8151–8161. <https://doi.org/10.1109/TPEL.2016.2521330>.

10. Jafari M., Saadatmand S., Shojaeighadikolaei A., Jafarishiadeh F., Ghasemi A., Alshawish A.M., Ahmadi R. - New Voltage Balancing Technique Based on Carrier-Disposition Pulse Width Modulation for Modular Multilevel Converter. 2020 IEEE Power Energy Conf. Illinois, **2020** (2020) 0–4. <https://doi.org/10.1109/PECI48348.2020.9064635>.

11. Joshi S.D., Ghat M.B., Shukla A., Chandorkar M.C. - Improved Balancing and Sensing of Submodule Capacitor Voltages in Modular Multilevel Converter. IEEE Trans. Ind. Appl. **57** (2021) 537–548. <https://doi.org/10.1109/TIA.2020.3026664>.

12. Nguyen M.H., Kwak S., Kim T. - Phase-Shifted Carrier Pulse-Width Modulation Algorithm with Improved Dynamic Performance for Modular Multilevel Converters. IEEE Access **7** (2019) 170949–170960. <https://doi.org/10.1109/ACCESS.2019.2955714>.

13. Wang K., Deng Y., Peng H., Chen G., Li G., He X. - An improved CPS-PWM scheme-based voltage balancing strategy for MMC with fundamental frequency sorting algorithm. IEEE Trans. Ind. Electron. **66** (2019) 2387–2397. <https://doi.org/10.1109/TIE.2018.2813963>.

14. Nguyen M.H., Kwak S.S. - A Novel Phase-shifted Carrier PWM and Voltage Balancing Control Scheme for Enhancing Dynamic Performance of Modular Multilevel Converter. IECON Proc. Industrial Electron. Conf. **2019** (2019) 6060–6065. <https://ieeexplore.ieee.org/document/8927214>.

15. Wang Z., Wang Y., Chen J., Hu Y. - Decoupled Vector Space Decomposition Based Space Vector Modulation for Dual Three-Phase Three-Level Motor Drives. IEEE Trans. Power Electron. **33** (2018) 10683–10697. <https://ieeexplore.ieee.org/document/8305640>.

16. Jacob J., Chitra A. - Field Oriented Control of Space Vector Modulated Multilevel Inverter fed PMSM Drive. Energy Procedia **117** (2017) 966–973. <https://doi.org/10.1016/j.egypro.2017.05.217>.

17. Nguyen P.C., Phan Q.D., Nguyen D.T. - A New Decentralized Space Vector PWM Method for Multilevel Single-Phase Full Bridge Converters. Energies **15** (2022) 1–25. <https://doi.org/10.3390/en15031010>.

18. Gateau G., Dung P.Q., Cousineau M., Do P.U.T., Le H.N. - Digital implementation of decentralized control for multilevel converter. Proc. 2017 Int. Conf. Syst. Sci. Eng. ICSSE **2017** (2017) 558–562. <https://ieeexplore.ieee.org/document/8030937>.

19. Dung Phan Q., Nguyen P.C., To H.P., Nguyen B.A., Le-Nguyen D.K., Nguyen-Huu K.M., Pham L.N. - Decentralized Capacitor Voltage Control of Flying Capacitor Multilevel Inverter. Proc. 2021 Int. Symp. Electr. Electron. Eng. **2021** (2021) 238–243. <https://ieeexplore.ieee.org/document/9418671>.

20. Phan Q.D., Gateau G., Nguyen P.C., Cousineau M., To H.P., Nguyen B.A., Veit L., De Milly R., Hillesheim M.M. - A fast, decentralized, self-aligned carrier method for multicellular converters. Appl. Sci. **11** (2021) 1–34. <https://doi.org/10.3390/app11010137>.

21. Beig A.R., Poshtan M., Kanukollu S. - Novel SVPWM based switching sequences for modular multilevel DC to AC converter. Conf. Proc. IEEE Appl. Power Electron. Conf. Expo. **2019** (2019) 1858–1864. <https://doi.org/10.1109/APEC.2019.8721773>.

22. López Ó., Álvarez J., Freijedo F.D., Yepes A.G., Malvar J., Fernández-Comesaña P., Doval-Gandoy J., Nogueiras A., Lago A., Peñalver C.M. - Multilevel multiphase space vector PWM algorithm with switching state redundancy applied to three-phase four-leg converters. IECON Proc. Industrial Electron. Conf. **2010** (2010) 568–575. <https://ieeexplore.ieee.org/document/5675220>.

23. Johansson, B., Osterberg, E. - Algorithms for Large Matrix Multiplications: Assessment of Strassen's Algorithm. M.S. thesis, Royal Institute of Technology (KTH), Stockholm, Sweden (2018).

24. López Ó., Álvarez J., Doval-Gandoy J., Freijedo F., Nogueiras A., Peñalver C.M. - Multilevel multiphase space vector PWM algorithm applied to three-phase converters. IECON Proc. Industrial Electron. Conf. **55** (2008) 3290–3295. <https://doi.org/10.1109/IECON.2008.4758487>.

## TÓM TẮT

### ĐIỀU KHIỀN CÁC BỘ BIẾN ĐỔI CÔNG SUẤT PHÂN TÁN BA PHA ĐA BẬC DÙNG SVPWM

Nguyễn Phú Công<sup>1,\*</sup>, Lê Khắc Sinh<sup>1</sup>, Phan Quốc Dũng<sup>2</sup>

<sup>1</sup>Trường Đại học Công Thương Thành phố Hồ Chí Minh

<sup>2</sup>Trường Đại học Bách Khoa Thành phố Hồ Chí Minh

\*Email: [congnp@huit.edu.vn](mailto:congnp@huit.edu.vn)

Bài báo này trình bày cách thức triển khai phương pháp điều chế độ rộng xung vec-tơ không gian phân tán (SVPWM) (DSVPWM) cho các bộ biến đổi công suất ba pha, đa bậc (TPMPC). Bộ biến đổi công suất ba pha được đề cập trong nghiên cứu này có cấu hình mạch bao gồm đa mô-đun cascade ghép nối tiếp trong mỗi pha. Mỗi mô-đun bao gồm một mạch động lực cascade và một bộ điều khiển cục bộ. Các bộ điều khiển cục bộ sẽ trao đổi thông tin hạn chế với các mô-đun lân cận, thông tin giao tiếp có thể là vị trí mô-đun theo hàng và theo cột, biến độ điện áp tham chiếu, tần số của điện áp tham chiếu. Phương pháp DSVPWM có thể được xem xét như là một kỹ thuật điều chế đa bậc, phương pháp có thể tự động điều chỉnh dựa trên số lượng mô-đun đang hoạt động trong hệ thống. Chương trình thực thi của mỗi mô-đun cục bộ cho thấy số lượng phép tính thấp hơn so với bộ biến đổi công suất sử dụng một bộ điều khiển trung tâm. Bộ biến đổi công suất đề xuất có thể tự động điều chỉnh cấu trúc động khi có lỗi xảy ra nhằm đáp ứng tính linh hoạt trong điều khiển và nâng cao tính liên tục cung cấp điện trong vận hành. Cấu trúc và giải thuật điều chế đề xuất được tiến hành đánh giá trên phần mềm mô phỏng Matlab/Simulink.

*Từ khóa:* Điều khiển phân tán, điều chế độ rộng xung vec-tơ không gian phân tán, bộ biến đổi công suất đa bậc, bộ biến đổi công suất nối tầng.